Intel 在过去数年间历经技术推进受阻、关键决策失误与竞争对手夹击,从曾经制程领先的产业霸主地位迅速滑落,不仅错失 AI 算力爆发的关键黄金期,更因此陷入财务亏损扩大与市占率持续流失的困境,一度面临分拆重组与企业存续能力备受质疑的严峻考验。然而,随着 Intel 于 CES 展出 Panther Lake 处理器并揭示 18A 制程的最新进展,公司在先进制程与产品路线上逐步展现实质突破,18A 能否成为带领 Intel 重返产业竞争核心、重塑长期竞争力的关键转折,成为市场高度关注焦点。

18A 制程介绍

制程定位与战略意义

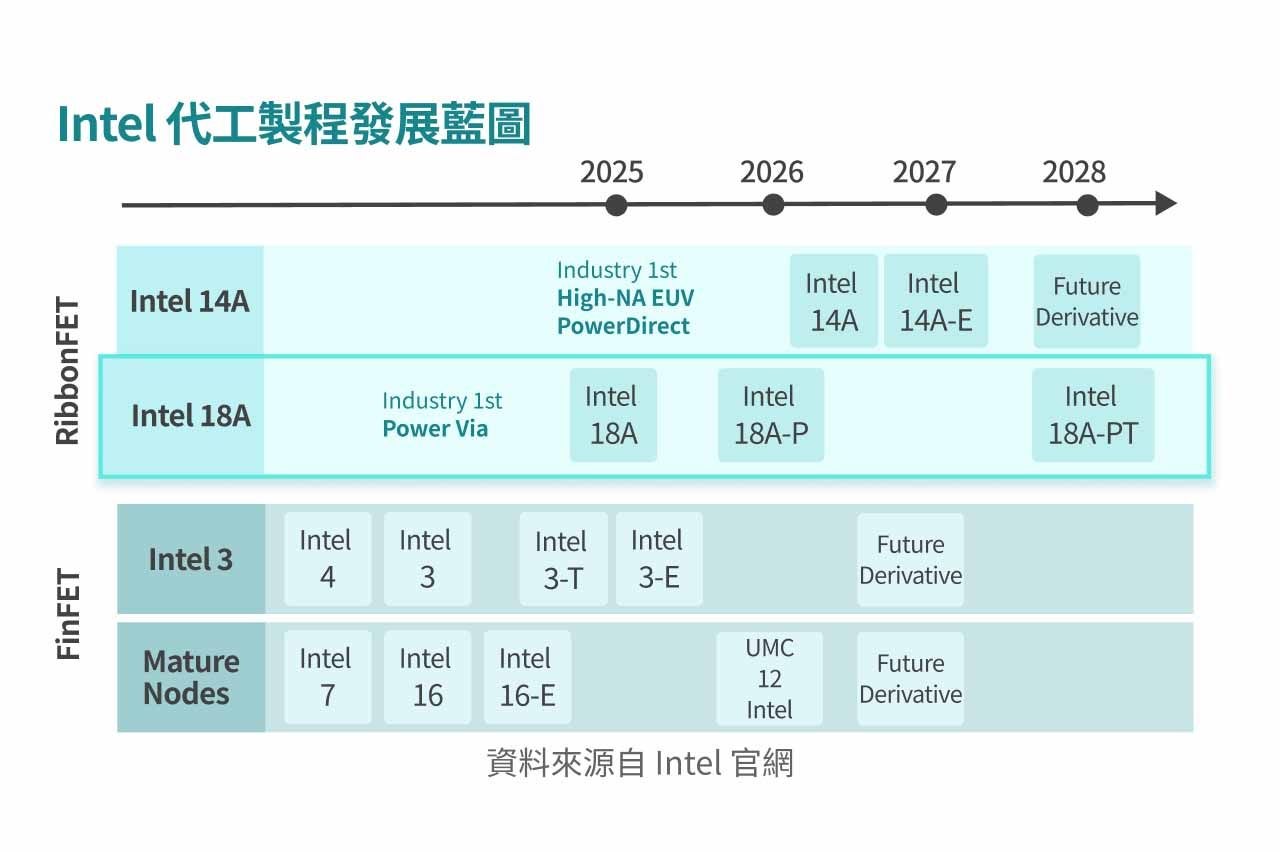

Intel 18A 在 Intel 制程蓝图中扮演关键角色,是 Intel 重返先进制程领导者地位的核心节点,透过 18A 制程,Intel 不仅试图在自有产品线上重建制程优势,也明确将其定位为代工服务(Intel Foundry Services, IFS)的旗舰节点,直接对标台积电(TSMC)于先进制程市场的领先地位。 18A 导入多项关键技术创新,包括 PowerVia 背面供电架构与 RibbonFET(GAA)电晶体设计,预期将在效能、功耗与面积等 PPA 指标上实现显著提升,从 Intel 的规划来看,18A 将成为北美最早具备量产能力的次 2 奈米级先进制程节点之一,对于希望分散供应链风险、并在美国本土生产先进晶片的客户而言,具备高度战略吸引力。

18A 技术细节

RibbonFET(GAA 环绕式闸极电晶体)

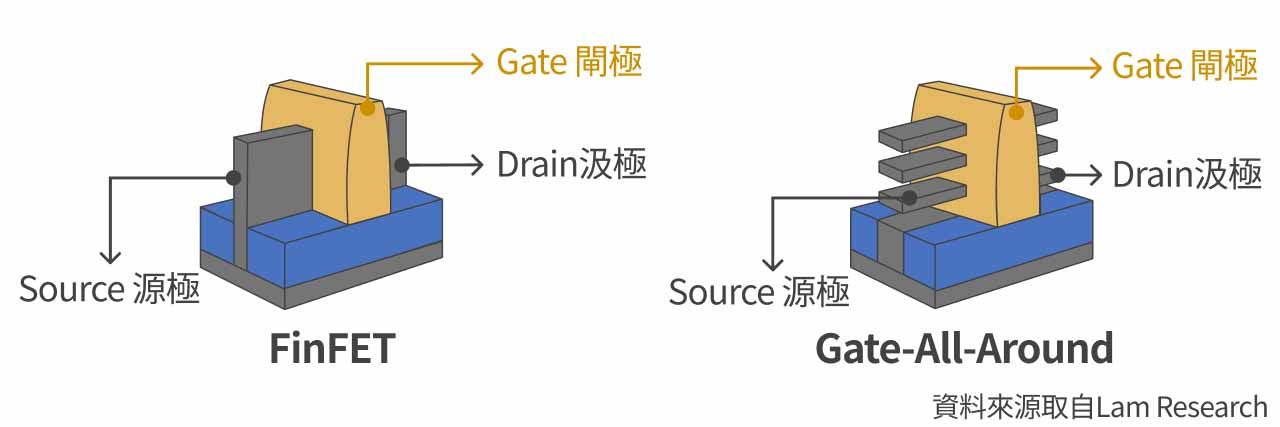

随着晶片越做越小,FinFET (鳍式电晶体)已经达到了物理极限,难以再微缩且漏电严重,像 RibbonFET 这种环绕式闸极电晶体(Gate-All-Around,GAA) 是摩尔定律得以延续的关键,它是半导体产业中的一项重大革命,旨在取代过去十多年来主流的 FinFET架构,使晶片能进一步微缩至 2 奈米及更先进的制程,环绕式闸极电晶体就像是把电晶体的导电通道从直立的鱼鳍变成了水平堆叠的丝带,并让控制开关的闸极完全包裹住这些丝带,这对未来 AI 运算和高效能资料中心至关重要。虽然这种最先进的电晶体统称为 GAA 技术,但各大厂的命名不同,而 RibbonFET 是 Intel 对于其 GAA 电晶体架构的称呼,三星将其称为 MBCFET (Multi-Bridge Channel FET),已在 3 奈米制程率先量产,台积电则统称为 GAAFET。

PowerVia(BSPDN 背面供电技术)

传统正面供电架构中电源与讯号线路高度混合,不仅造成金属层拥塞、也使电阻与电压下陷问题日益严重,进而影响整体效能与能耗表现,为解决此一问题,Intel 推出业界首创的 PowerVia 背面供电网路(BSPDN),成为 18A 制程世代的核心技术之一。PowerVia 的设计核心在于将电源供应网路由晶片正面完全移至背面,并在标准单元中导入奈米级穿孔(Nano-TSVs),使电力能以更直接、低阻抗的方式输送至电晶体,透过电源与讯号线路的彻底分离,释放正面金属层空间能改善布线壅塞并提升设计弹性,同时大幅减少电压下陷(Voltage Droop)。

在效能表现上,PowerVia 可使标准单元使用率提升约 5% 至 10%,并带来最高约 4% 的 ISO 电源效率提升;此外,由于前段金属层 RC 效能改善约 12%,加上穿孔电阻降低最多可达 49%,整体电源完整性明显优于过往架构;在逻辑库配置方面,Intel 18A 提供 180CH 高效能版与 160CH 高密度版,以兼顾不同应用需求。这项技术 Intel 采取了领先业界的策略,先在 Intel 3 制程上开发 PowerVia 测试晶片并取得成功,这使 18A 在量产这项革新技术时具备更高的成熟度。

微影技术

在微影技术方面,Intel 18A 制程的成功关键在于其对 High-NA EUV(高数值孔径极紫外光) 设备的先行部署。 身为 ASML 该设备的首波客户,Intel 在 18A 研发阶段便积累了关键的曝光参数与设计规则,这为其后续 14A 的全面领先奠定了物理基础。尽管 18A 在初期量产阶段为了兼顾产能与成本,会采取标准 0.33 NA EUV 多重曝光与 High-NA 设备并行的灵活策略,但率先掌握 High-NA 技术让 Intel 在 2 奈米以下的微缩竞赛中,相较同业拥有更长的设备磨合经验与技术数据,这对于实现更精细的电路图案与减少制程步骤具有决定性意义。

Omni MIM 电容器应用 (非 18A 独有)

在追求高效能运算的过程中,感应式功率下降一直是维持电压稳定的主要挑战,因此 Intel 在 18A 制程进一步导入了新一代高密度金属-绝缘体-金属(MIM)电容器,这些微型电容器广泛分布在电路层中,扮演着关键的储能与平衡角色,能在电流急剧波动时提供即时缓冲,大幅抵销功率波动,进而提升晶片在高负载下的运作稳定性,这种对电力稳定度的极致追求,是维持 2 奈米等级精密电路正常运作的核心基础,确保供给电晶体的电力平稳且无杂讯干扰,对于生成式 AI 等现代工作负载而言至关重要,因为 AI 运算往往具有极高的突发强度,需要极其精准且即时的电力缓冲来确保系统不间断运作、让电力传输更加纯净。

先进封装与 3D 晶片堆叠技术 Foveros (非 18A 独有)

先进封装已成为延续摩尔定律、提升运算效能的关键技术,而英特尔的 Foveros 3D 封装技术,透过垂直堆叠方式,将多个具备不同功能的晶片模组整合至单一系统级晶片(SoC)中,大幅提升设计弹性与扩充性。 进一步结合 PowerVia 以及 EMIB 等技术,Foveros 建构出高度整合的异质封装平台,使晶片能在有限的封装空间内释放更高的运算效能与频宽潜力。值得注意的是,目前台积电与三星亦已推出各自的 3D 封装解决方案,因此对英特尔而言,Foveros 虽是核心技术之一,但并非独占或领先同业的制程门槛。

18A 制程应用

18A 的实战价值将由 2026 年上半年的 Clearwater Forest (Xeon 6+ 处理器) 正式启动,该处理器不仅拥有 288 个高效率核心,更透过 PowerVia 与 Foveros 实现了异质整合的极致,预期 IPC 较前代提升 17%。随后的消费级 Panther Lake 处理器则将验证 18A 在行动端的高能效表现,这些产品不仅是 Intel 自家产品线的重生,更是向代工客户展示其能在美国本土实现次 2 奈米级稳定产出的旗舰标竿。

市场竞争:其他晶圆厂的发展蓝图

除 Intel 在先进制程上出现突破外,台积电与 Samsung 亦已在 2nm 制程上取得实质性进展,两家公司皆于 2025 年启动量产,显示先进制程竞赛为多方并进、节点密集推进的全面竞争格局。

台积电

台积电 N2 制程于 3Q25 启动量产,并将逐步推出 N2 系列,提供客户横跨消费性电子、企业运算与 AI 应用等多元场景的产品选择:其中 N2 主要适用于行动装置与穿戴式设备,N2P 则在效能提升与功耗降低方面进一步优化,设计重心聚焦于旗舰级智慧型手机与高效能笔电;至于 A16 节点预期将整合更先进的封装技术,锁定高效能运算与云端 AI 等具高度可扩展性的架构应用。

| 效能 | 功耗 | 晶片密度 | 量产时间 | 应用 | |

|---|---|---|---|---|---|

| N2 (vs N3E) | 提升 10-15% | 降低 25-30% | 提升 15% | 3Q25 | 行动装置 |

| N2P (vs N2) | 提升 5-10% | 降低 5-10% | 与 N2 相同 | 2H26 | 智慧型手机 |

| N2X (vs N2) | 提升 5-10% | - | - | 2027 | - |

| A16 (vs N2P) | 提升 8-10% | 降低 15-20% | 提升 7-10% | 2H26 | 高效能运算 |

Samsung

Samsung 的 2nm 制程命名为 SF2,2025 年进入量产,初期聚焦于行动处理器晶圆生产,首项导入产品为自家 Exynos 2600 晶片;其后于 2026 年延伸发展为 SF2P 制程技术,效能较前一代提升约 12%,功耗降低约 25%,市场传出 Tesla AI6 晶片有望采用 SF2P 投片生产。同年 Samsung 亦同步规划推出锁定高效能运算与人工智慧应用的 SF2X 制程;至于 SF2A 制程则以车用处理器为主要应用方向,预计于 2027 年正式进入量产阶段。

Intel 与 Samsung、台积电 2nm 制程比较

| Intel | 台积电 | Samsung | |

|---|---|---|---|

| 制程名称 | 18A | N2 | SF2 |

| GAA 架构 | RibbonFET | Nanosheet | MBCFET |

| 晶背供电技术 | 已导入 (PowerVia) | A16 导入 (Super Power Rail) | 2027 导入 (类似 PowerVia) |

| 效能 | 提升 25% (vs Intel 3) | 提升 10-15% (vs N3E) | 提升 5% (vs SF3) |

| 功耗 | 降低 36% (vs Intel 3) | 降低 25-30% (vs N3E) | 降低 25% (vs SF3) |

| 良率 | 50% | 约 90% | 50% |

| 量产时间 | 2H25 | 3Q25 | 2025 |

| 策略重点 | 技术大幅革新,争取制程领先 | Roadmap 稳定推进,确保良率与客户需求 | 克服良率挑战,扩大客户基础 |

| 优势 | 首先导入晶背供电技术,供电与密度优势显著 | 技术成熟度高、生态系完整 | 较早导入 GAA 架构,具降低成本潜力 |

| 潜在挑战 | PowerVia 量产成熟度及整合风险 | - | 良率爬升速度、市场竞争压力 |

| 采用客户 | 自家 Panther Lake 处理器 | 联发科、QCOM、AAPL 等 | 自家 Exynos 2600 晶片 |

Intel 18A 以 RibbonFET 搭配 PowerVia 晶背供电作为主要差异化,相较 Intel 3 可带来约 25% 效能提升与 36% 功耗降低,并试图以供电效率与电晶体密度优势重夺制程领先地位。 然而,从量产节奏与制造成熟度观察,Samsung SF2 已于 2025 年率先量产,台积电 N2 亦于 3Q25 进入量产,时程皆早于 Intel 18A 规划的 2H25;其中,台积电 N2 在良率表现与整体效能上均明显领先 18A,显示其技术成熟度与生态系优势具备较高确定性,且已获得多家一线客户订单肯定。相较之下,Samsung 虽具备较早导入 GAA 架构的经验并主打成本潜力,但现阶段仍须克服良率爬升速度与激烈市场竞争的双重挑战。 整体而言,Intel 18A 的关键胜负仍在于 PowerVia 于量产阶段的整合成效与良率提升速度,唯有顺利跨越量产成熟度风险,才能在先进节点竞局中实质缩小与台积电、Samsung 的差距,并重塑长期竞争力。

市场看法与展望

18A 制程为 Intel 代工业务的关键节点,亦是市场高度关注的核心焦点。 近年来 Intel 在 PC CPU 市场承受显著竞争压力,主因在于 AMD 借助台积电先进制程,在效能与功耗表现上持续拉开差距;受限于自有制程推进落后,Intel 过去主流的 Raptor Lake 仍停留在 10 奈米节点,产品竞争力明显不足,迫使公司于 Lunar Lake 与 Arrow Lake 世代大幅转向台积电代工以维持产品表现。Panther Lake 则标志策略上的重要转折,作为首款基于 Intel 18A 制程的大规模量产晶片,相较前代展现显著技术突破,官方数据显示其效能较 Lunar Lake 提升约 60%,游戏效能更大幅成长约 77%。

对 Intel 而言,Panther Lake 不仅是产品世代更新,更攸关其代工业务能否实现长期且可持续经营,其量产稳定性与能效表现将直接影响潜在客户的导入意愿,包括联发科与 Qualcomm 等设计商皆持续关注其实际量产成果。 市场亦传出 Broadcom 可能将部分 ASIC 需求分配至 Intel 18A-P 制程,Apple 亦正评估于 2027 年 M 系列晶片导入效能优化版的 Intel 18A-P;若 Panther Lake 能顺利验证制程成熟度与能效竞争力,Intel 争取关键一线客户的成功机率将显著提升。在台积电先进制程产能长期吃紧的结构性背景下,18A 乃至后续的 14A 制程,具备成为潜在重要替代方案的战略价值。

总结:技术突破与量产执行的关键时刻

整体而言,Intel 18A 不仅是一个制程节点的推进,更是 Intel 技术路线、代工战略与长期竞争力能否重塑的关键。 18A 透过 RibbonFET 与 PowerVia 的同步导入,在电晶体架构与供电方式上实现跨世代革新,使 Intel 在技术设计层面重新具备与台积电、Samsung 正面竞逐次 2nm 世代的能力。然而,从产业现实面观察,台积电 N2 以更高良率与成熟生态系率先量产,Samsung 亦抢先卡位行动与特定应用市场,显示先进制程竞争已转为「量产执行力与客户信任」的全面比拚。

对 Intel 而言,Panther Lake 与 Clearwater Forest 的量产表现,将直接决定 18A 是否仅止于技术展示,抑或真正转化为可规模化的代工节点;若能成功验证良率、能效与交付稳定度,18A 乃至后续 14A 将有机会在台积电产能长期吃紧的结构下,成为一线客户的实质替代选项。反之,若量产成熟度不如预期,Intel 在先进制程竞局中的追赶时间窗将进一步收敛。最终,18A 的成败不仅关乎 Intel 代工业务,更将左右全球先进制程供应格局是否出现真正的多极化。