随着摩尔时代持续推进,摩尔定律逐步逼近物理极限。晶片尺寸不断缩小,制程节点已从奈米迈向埃米等级;随着电晶体密度持续提高、堆叠层数不断增加,传统 2D 晶片架构逐渐逼近极限,制程也正加速朝 3D 化发展。在此架构演进下,过去并非核心问题的「供电」开始浮上台面,成为限制制程持续微缩的关键瓶颈之一。一方面,电源布线占据大量晶片正面空间,压缩逻辑电路的布局弹性;另一方面,电力在传输过程中产生的 IR drop 与能量损耗,也直接限制效能与能效表现。

因此,晶片供电逐渐从辅助设计,转变为延续摩尔定律的重要工具。主要三大晶圆代工厂——台积电、三星与英特尔——皆陆续提出「晶背供电」(BSPDN, Backside Power Delivery Network)技术,透过将供电网路移至晶片背面,改善供电效率,同时释放晶片正面空间,以承载更多高密度逻辑电路。 本文将聚焦于台积电的晶背供电技术发展。根据目前规划,台积电预计于2026 年第三季A16 制程中导入 BSPDN,并将其视为先进制程节点中不可或缺的关键技术之一。

技术背景:晶片微缩进程面临的挑战

目前晶片微缩所面临的核心挑战,主要可归结为两大问题:其一是可用布线空间持续压缩,其二是效能提升逐渐遭遇结构性的瓶颈。 在传统逻辑晶片架构中,晶片通常由基板、电晶体层,以及位于最上方的多层金属布线层所构成。随着制程节点不断推进,在既有供电与布线架构未出现根本性改变的情况下,这两项限制被进一步放大,成为制约技术演进的关键因素。

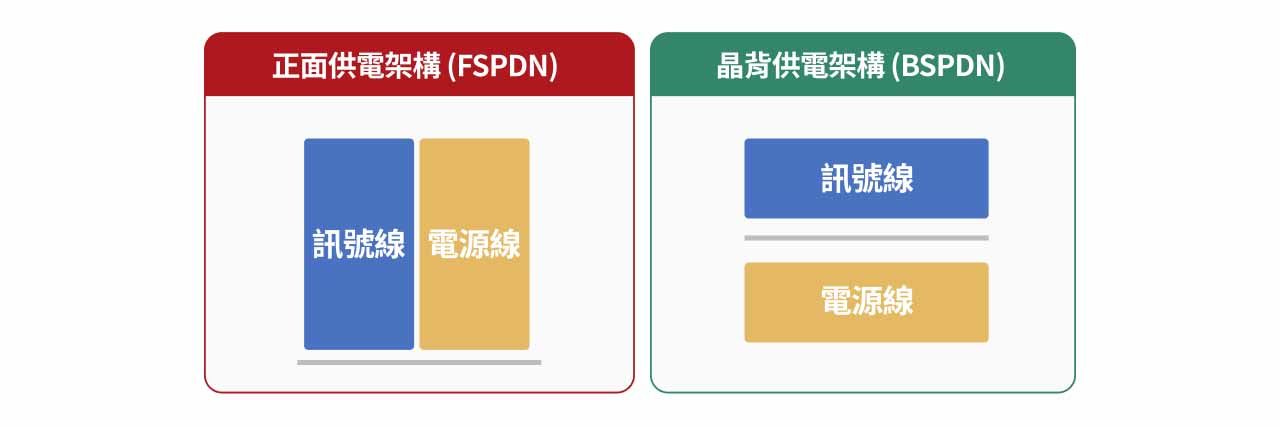

现行主流采用的是正面供电架构(FSPDN)。 电流由晶圆正面引入,必须穿越约 60~70 层金属布线,才能一路传递至最底层的电晶体。简单来说,就像是从一栋 70 层的大楼顶楼拉电线,一路拉到一楼;随着制程持续微缩、线宽变窄,导线电阻不断上升,压降(IR Drop)问题也随之恶化,同时带来更高的功耗与干扰风险,逐渐成为效能提升的瓶颈。

在金属布线结构中,依功能大致可分为两类路径: 一类是讯号线,负责传输逻辑讯号,电压与电流相对微弱,但路径复杂且数量庞大; 另一类则是电源线,主要任务是将外部电流导入电晶体,提供其开关所需的能量。

然而,在传统正面供电架构下,电源线必须与大量讯号线共用有限的正面布线空间。当制程持续微缩、金属层数增加时,这种空间竞争便具体表现在以下几个工程层面的问题上:

- 随着线宽缩小,导线电阻上升,使压降(IR Drop)持续恶化

- 底层电晶体实际可取得的电压不足,能量损失限制其效能发挥

- 电源线与讯号线距离过近,电磁干扰加剧,进一步推升功耗与设计复杂度

技术介绍:晶背供电是什么?

晶背供电是将原先配置于晶片正面的电源供应路径移转至晶片背面,借此释放正面同时承载讯号线与电源线所占用的布线空间。

晶背供电的核心主要建立在两项关键技术之上:埋入式电源轨(Buried Power Rail, BPR)以及奈米矽穿孔(Nano Through-Silicon Via, n-TSV)。

- 埋入式电源轨: 是将垂直方向的电源线(VDD、VSS)直接嵌入基板内部,使供电路径不再占用晶片正面的金属布线层,并与后段制程(Back End of Line, BEOL)中负责讯号传输的金属线路完全分离。这样的设计,等于在结构上将「供电」与「讯号」两套系统拆开处理,避免彼此争夺有限的布线空间。

- 奈米矽穿孔: 是在基板中垂直钻设高密度、奈米尺度的通孔,并于孔内填充导电材料,形成由晶片背面直达电晶体层的垂直导电通道。透过这些奈米矽穿孔(n-TSV),电源与接地可以直接由基板背面导入,大幅缩短供电路径,并有效降低电阻与压降。

综合而言,BPR 负责在基板内建立稳定的电源骨干,而 n-TSV 则扮演连接背面供电与前端电晶体的关键桥梁,使得「从背面供电」在先进逻辑制程中具备实际可行性。

台积电 Super Power Rail 晶背供电技术

与英特尔先导入的 PowerVia 晶背供电技术 不同,台积电的晶背供电技术为 Super Power Rail (SPR),台积电采用 Back-to Back,直接利用晶背供电其中也是目前现有三种中最复杂的。

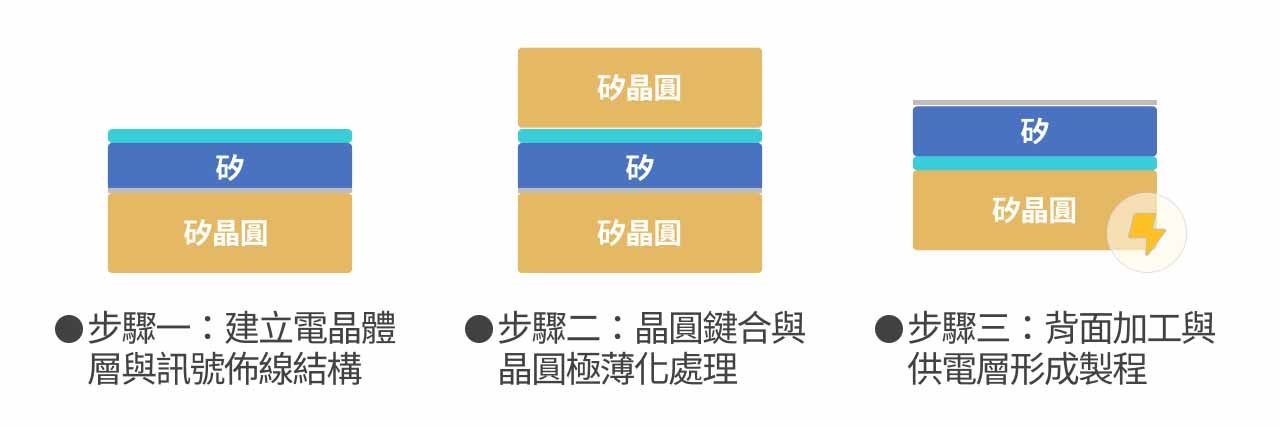

步骤一:建立电晶体层与讯号布线结构

制程首先以一片厚度约 600,000 奈米(600 µm) 的矽晶圆作为基底,在其上方建构约 100 奈米 厚度的电晶体层,并进一步堆叠约 500 奈米 厚度的讯号导线区。 与传统制程不同的是,此阶段仅需构筑讯号导线,而不再同时建立电源线,因为在晶背供电架构中,电源分配网路将改由晶圆背面实现,使前段金属层能专注于讯号传输功能。

步骤二:晶圆键合与晶圆极薄化处理

当讯号线区完成后,需将整片晶圆与另一片同样厚度约 600,000 奈米 的矽晶圆进行 Wafer Bonding,上方晶圆即作为承载晶圆(Carrier Wafer)。 此步骤的目的在于,为后续背面加工与极端薄化提供必要的机械支撑。由于原始晶圆本体将从 600 µm 大幅削薄,最终仅剩电晶体层,整体结构几乎丧失刚性,若缺乏外部支撑,将无法承受设备夹持、搬运以及后段制程所产生的热与机械应力。

步骤三:背面加工与供电层形成制程

完成键合后,晶圆进入研磨与化学机械平坦化(CMP)阶段,将原始矽基底完全去除,只保留前段制程所形成的电晶体层,此时晶圆已翻转,使原本的背面朝上。 接着透过矽穿孔技术,在电晶体底部开孔以建立背面供电通道,并于其上沉积约 500 奈米 厚度的电源金属层,最终完成晶背供电层的建构。

晶背供电中的关键步骤:晶圆薄化与再生晶圆应用

在晶背供电与先进封装制程中,晶圆薄化是不可或缺的关键步骤。由于晶片电路皆制作于晶圆正面,前段制程必须使用具备足够厚度与结构强度的晶圆,以承受高温与多道制程要求;然而,当电路制作完成后,若晶圆维持过厚,将限制后续背面供电布线、散热效率与封装堆叠设计。因此,实务上需于主要制程完成后,自晶圆背面进行极度薄化,以满足晶背供电与先进封装对厚度与结构配置的要求。

然而,晶圆在薄化后结构极为脆弱,已无法承受后续制程与搬运需求,使晶圆键合成为必要前置步骤。透过暂时键合,将制程晶圆固定于承载晶圆上,可提供必要的机械支撑,确保薄化与背面制程的稳定性与良率。

在此流程中,再生晶圆同时被广泛应用于承载晶圆与制程测试晶圆。 一方面,承载晶圆不需具备产品功能,只需满足平整度与结构强度要求,再生晶圆即可胜任并可重复使用;另一方面,键合、薄化与背面制程导入前后,需大量进行制程验证与设备校正,测试晶圆用量大幅增加,使用再生晶圆有助于有效控制成本。

整体而言,晶圆薄化决定先进制程与晶背供电的可行性,晶圆键合确保制程稳定,而再生晶圆则支撑其量产与成本结构,三者相互依存、缺一不可。

再生晶圆

再生晶圆(Reclaimed Wafer)是指将曾投入半导体制程、但结构仍完整的矽晶圆,经由去膜、研磨、CMP 抛光与缺陷检测等程序重新加工后,再次用于制程监控、测试或假片用途。 由于不直接作为最终产品晶片,其成本明显低于原生晶圆,却能满足晶圆厂在制程稳定性与设备校准上的需求。

在晶背供电制程中,再生晶圆常被应用于承载晶圆,当元件晶圆因电性连接需求进行背磨,厚度降至约 100 微米,甚至进一步薄化至 10 微米以下时,晶圆的机械强度将显著下降,于搬运或高温制程过程中容易产生破片或严重翘曲。此时,承载晶圆的核心功能在于提供稳定且可靠的支撑基板,使超薄元件晶圆得以维持结构完整性,并顺利完成后续微影、金属沉积、CMP 与干式蚀刻等制程,同时降低因晶圆破裂或翘曲所造成的良率损失。整体而言,在先进封装与高阶 AI 晶片制造中,承载技术的成熟度已直接影响整体制造成本、良率表现与产品稳定性。

制造流程

1. 分类(Sort) 此步骤的主要目的,是在再生制程开始前,先筛选不适合的晶圆,避免金属污染进入再生产线。所有进料晶圆皆会逐片检查,包含外观是否有缺陷、晶圆种类,以及基本的材料与结构特性。检查结果将用来判断晶圆是否适合再生,并决定后续应采用的再生制程流程。

2. 去膜(Strip) 去膜的目的是将晶圆表面原有的各类薄膜移除,让晶圆能顺利进入后续的再生制程。 实际采用的去膜方式,会依晶圆的来料状况进行调整,通常于自动化的湿式批次清洗设备中完成。常见使用的处理药液包含 SPM(硫酸+过氧化氢)、高浓度 HF 蚀刻,以及 碱性蚀刻(如 KOH),并依不同薄膜类型选择搭配使用。若晶圆表面含有金属薄膜,则需增加额外的前处理步骤。此阶段最重要的重点,在于确保薄膜完整去除,同时避免不同晶圆之间发生交叉污染。

3. 研磨与修边(Grinding & Edge Treatment) 对于中间含有绝缘层、结构较厚的 SOI 晶圆,或需移除特定薄膜的情况,通常会先进行研磨制程,并同时搭配修边与边角圆化处理,以改善晶圆外型与制程稳定性。 研磨的优点是材料去除速度快,但在厚度与表面均匀性上较难控制,因此在研磨完成后,会再透过 CMP 进行平滑处理与最终抛光,以提升表面品质并确保晶圆平整度,使其符合后续制程需求。

4. 抛光(Polish) 抛光可分为单面或双面抛光,通常结合化学与机械方式进行。其中,双面抛光可有效降低 TTV(总厚度变异),使晶圆厚度更为一致。 完成抛光后,晶圆表面会回到裸矽状态,整体厚度也会低于原始晶圆,并可进入最终清洗阶段。不过抛光过程中,表面可能残留抛光浆料、微粒或金属污染,因此必须在后续清洗制程中彻底去除。

5. 清洗(Clean) 最终清洗通常在自动化批次湿式清洗设备中完成,并可于同一套设备中依序进行多个清洗步骤。 清洗流程采用标准 RCA 清洗,包含: SC-1(H₂O/NH₄OH/H₂O₂):用于移除晶圆表面的粒子与残留物 SC-2(H₂O/HCl/H₂O₂):用于降低金属污染 经过清洗后,晶圆表面的金属浓度可降至 5×10¹⁰ atoms/cm² 以下,实务上通常可达 1×10¹⁰ 以下。最后再透过表面张力干燥完成整个清洗流程。

6. 检测(Inspection) 再生完成后,晶圆会依厚度与表面缺陷数进行分类与分级。一般测试晶圆需符合 0.12 µm LPD(Light Point Defect,光点缺陷)小于 50 颗的典型规格。

由于测试晶圆常被用于设备调校与制程问题排查,其缺陷表现会直接影响判断结果,因此缺陷控制是再生制程中相当关键的一环。

再生晶圆的优势

- 降低生产成本:再生晶圆的使用成本约为新晶圆的 20–30%,可有效降低测试与非关键制程的整体支出

- 减碳与永续:相较于新晶圆制造,再生流程在能耗与用水量上可减少约 60–80%,符合半导体产业的减碳与 ESG 发展方向

- 提升制程稳定与良率:透过大量再生晶圆进行设备验证与制程测试,有助于提前发现制程偏移,降低量产风险

先进制程推升再生晶圆需求

随着制程节点持续微缩,再生晶圆的需求明显放大。升阳半导体在法说会中指出:

- 5 奈米制程:投片 10 万片,约需 10 万片再生晶圆

- 3 奈米制程:再生晶圆需求提升至约 2.2 倍

- 2 奈米制程:再生晶圆需求进一步拉高至 2.6 倍以上

这代表制程愈先进,对测试、校正与制程控制的依赖程度愈高,再生晶圆已不再只是辅助材料,而是支撑先进制程运作的重要基础资源。 再生晶圆原本只是前段制程中的测试耗材,但随着制程节点持续推进与先进封装需求提升,其角色已转变为支撑制程稳定、降低成本,并支援超薄元件晶圆制造的重要基础材料。

再生晶圆原本只是前段制程中的测试耗材,但随着制程节点持续推进与先进封装需求提升,其角色已转变为支撑制程稳定、降低成本,并支援超薄元件晶圆制造的重要基础材料。

晶圆薄化

晶圆薄化(Wafer Thinning)是指在半导体制造流程中,于前段制程完成后,从晶圆的背面移除材料,使晶圆整体厚度降低。 这个步骤的目的在于因应晶片小型化与先进封装需求,让晶片能够做到更薄、更小,并支援堆叠与高密度整合,进而应用于体积受限但效能要求更高的电子产品。

晶圆薄化的优势

晶圆薄化不只是为了变薄,而是直接影响整体封装与效能表现,主要效益包括:

- 散热表现提升:晶片变薄后,热较容易传导,有助于高效能晶片长时间运作的稳定性

- 封装尺寸缩小:较薄的晶片可支援更高密度的封装与堆叠,有利于装置小型化

- 降低内部应力:厚晶片在温度变化下容易累积内部应力,薄化后可降低裂损风险

- 电性表现改善:结构距离缩短,有助于提升高频讯号与整体电性效率

- 切割与封装良率提升:薄化后的晶圆较不易在切割与封装过程中产生崩边或损伤

晶圆薄化的限制

由于积体电路制作于晶圆正面,晶圆于前段制程阶段需维持高度的平整度与结构稳定性,因此晶圆薄化仅能于主要制程完成后进行,并透过背面逐步移除材料的方式达成目标厚度。 在此过程中,晶圆平整度的控制成为影响制程良率的关键因素。

随制程节点持续微缩,晶圆薄化对背面研磨均匀性与平坦度的要求大幅提高,使化学机械平坦化制程的重要性进一步提升。其中,钻石碟作为研磨垫修整的核心耗材,直接决定研磨条件的稳定性与一致性,其精度与耐用度将影响晶圆薄化品质与最终制程良率,在先进制程中扮演不可替代的关键角色。

常见的晶圆薄化方式

实务上,晶圆薄化并非只依赖单一方法,而是依制程需求进行搭配使用,常见方式包括:

- 机械研磨:最常见的薄化手段,透过研磨设备快速去除背面材料,通常分为粗磨与细磨

- 化学机械研磨(CMP):在研磨过程中搭配化学药液,改善表面平坦度与品质,但成本与制程要求较高

- 化学蚀刻:利用化学方式进一步移除材料,常作为研磨后的表面修整

- 电浆相关技术:透过电浆与化学反应进行薄化,特色是厚度均匀性较佳,常用于先进制程

在台积电的晶背供电技术中主要用到机械研磨和化学机械研磨。

晶圆薄化的核心概念在于先以较厚的晶圆完成电路制作,再从背面进行薄化,以同时兼顾制程稳定性与最终产品对小型化、散热与先进封装的需求。随着先进封装与高效能晶片发展,晶圆薄化已成为不可或缺的关键制程之一。

晶背供电技术比较:台积电 vs. Intel vs. Samsung

![台积电、三星、英特尔logo图。]

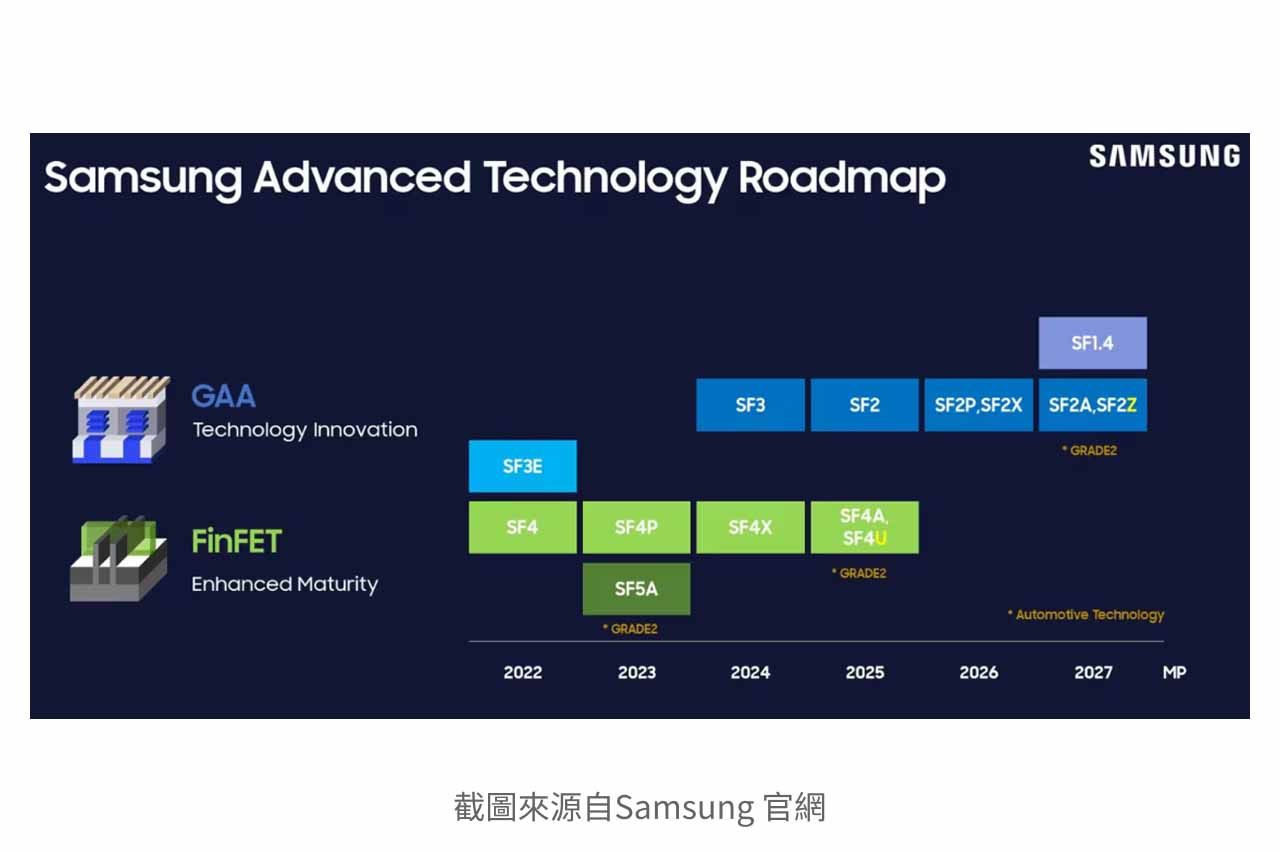

竞争格局呈现三强鼎立,除了台积电使用晶背供电技术以外,英特尔试图透过率先量产来重夺技术领导地位,三星则紧随其后,预计于 2027 年量产。虽然晶背供电的总体目标一致,但各家厂商在具体实作路径上存在显著差异,主要体现在电源接入点(Tap Point)与制造流程的复杂度上。

技术导入进度

英特尔 PowerVia 的商用化进度

英特尔的 PowerVia 是其 Intel 18A 制程的关键组成,与 RibbonFET(GAA)同步导入,目标在于透过背面供电降低 IR drop 并释放前端布线资源。 英特尔于 2026 年 CES 正式发布 Core Ultra Series 3(Panther Lake),该系列为首批采用 18A 制程的客户端处理器,象征 PowerVia 从研发阶段迈入实际商用产品周期。

就制程成熟度而言,18A 目前仍处于量产爬坡阶段。英特尔管理层指出,现阶段良率已可支撑产品出货,但距离理想的成本结构仍有差距,显示背面供电相关制程仍是成本与良率管理的挑战。 所以PowerVia 已进入可商用阶段,但其长期经济性与对 PPA 的全面影响,仍有待更多量产数据验证。策略层面,Intel 18A 与 PowerVia 亦被视为其晶圆代工服务的重要差异化技术。虽然外部客户的实际量产案例尚未公开,但美国本土制造的特性,使其在供应链安全与政策导向应用上具备一定战略价值。

三星 SF2Z 的未来布局

三星的 SF2Z 为 2 奈米制程家族中整合背面供电的进阶版本,主要锁定 HPC 与 AI 应用,量产时程预计落在 2027 年。 SF2Z 建构于三星已量产多代的 MBCFET(GAA) 架构之上,延续其在奈米片电晶体上的制程经验。

SF2Z 的核心目标在于,透过背面供电改善高功率密度设计下的供电瓶颈,进一步提升整体 PPA 表现。不过,截至目前为止,三星尚未公开具体的效能或功耗改善数据,其实际效益仍有待量产后验证。相较竞争对手,SF2Z 的主要风险在于导入时间较晚,能否以足够的 PPA 优势与良率表现弥补时程落后,将是其市场竞争力的关键。

Intel PowerVia 制造流程的关键差异

Intel 为最早导入晶背供电技术的厂商,而台积电在技术路线上,则与 Intel 展现出多项显著差异:

PowerVia 在前段制程预埋 Nano-TSV

与台积电 Super Power Rail 由背面直接建立电源接触不同,Intel PowerVia 的核心设计在于前段制程即同步预埋 Nano-TSV(奈米级矽穿孔)。 这些 Nano-TSV 在电晶体制作阶段便已形成,但初期仅为「盲孔」结构,尚未贯穿晶圆。此作法与封装层级 TSV 明显不同,其奈米级尺寸与电晶体同步对位的特性,使电源垂直连接能在极小面积内完成,避免侵蚀标准单元布局空间。相较之下,台积电 Super Power Rail 并未采用 TSV 类结构,而是以背面金属层直接连接电晶体端点,两者在电源垂直导通路径上属于不同工程哲学。

PowerVia 将电源完全移至晶圆背面,使正面金属层专注于讯号传输

在 PowerVia 架构下,Intel 将电源与接地路径完全移至晶圆背面,使正面所有金属层得以专注于讯号传输。这一点与台积电仍需在正面层次中保留部分供电结构的作法不同。 PowerVia 因此在正面获得更高的讯号布线自由度,能有效降低绕线、串扰与 RC 延迟,这也是 Intel 强调其在逻辑密度与时脉提升上的重要基础。

PowerVia 的关键风险在于薄化过程中需精准露出预埋的 Nano-TSV

Intel PowerVia 同样需要经历晶圆翻转、键合至载体晶圆并进行极致减薄,但其风险集中点与台积电不同。由于 Nano-TSV 早已预埋于晶圆内部,减薄工程的关键在于精准停止于 TSV 顶端,确保 TSV 能被完整露出而不受损。 此步骤对厚度控制与翘曲管理的要求极高,也使 PowerVia 的良率与成本高度取决于键合与研磨精度。而台积电 Super Power Rail 面临的挑战更多在于背面对准与直接接触源极/汲极的制程控制,两者风险结构并不相同。

PowerVia 采用三段式供电架构

在晶圆背面,Intel 建立专属的粗线宽背面电源网路,并透过 Nano-TSV 将电力垂直传输至电晶体接触层。此一「背面电源 → TSV → 电晶体」的三段式结构,是 PowerVia 的核心特征,也与台积电采取「背面金属直接接触电晶体端点」的设计形成鲜明对比。 PowerVia 的优势在于 TSV 提供高度可控的垂直导通路径,而代价则是额外的制程步骤与结构复杂度。

晶背供电技术综合比较

在背面供电逐步走向量产落地的过程中,台积电、Intel 与 Samsung 已分别选择不同的实现路径,反映其在制程整合能力、风险承受度与产品节点策略上的差异。

- Intel 率先于 18A 节点导入 PowerVia,强调设计连续性与量产可行性

- Samsung 则在 GAA 架构下结合背面供电与既有埋入式电轨设计,试图在密度与效能间取得平衡

- 台积电的 A16 Super Power Rail 则被视为最具前瞻性的方案,潜在微缩效益最高,但同时伴随较高的制程复杂度与量产挑战。

以下比较表从量产时程、电晶体与供电架构、连接机制,以及效能与风险面向,对三家先进节点的晶背供电策略进行对照,借此评估各大厂在下一世代先进制程竞争中的技术定位。

| 比较项目 | Super Power Rail | PowerVia | BSPDN |

|---|---|---|---|

| 公司 | 台积电(TSMC) | 英特尔(Intel) | 三星(Samsung) |

| 量产时间 | 2026 年下半年(2H26) | 2025 年下半年(2H25) | 2027 年 |

| 效能表现 | 1. 在相同电压下,时脉提升约 10% 2. 在相同频率与电路复杂度下,功耗降低约 15%–20% 3. 电晶体密度提升约 7%–10% | 1. 晶片多数区域的标准单元利用率可超过 90% 2. 平台电压下陷(Voltage Droop)改善约 30% 3. 频率提升约 6% | 1. 晶圆面积使用率降低约 14.8% 2. 布线长度缩短约 9.2%,有助于降低电阻、提升电流传输能力 |

| 技术特点 | 1. 导入于 A16 制程,并与 GAA 电晶体架构结合 2. 将电源传输线直接连接至电晶体源极/汲极(S/D),显著提升晶片供电效率 | 1. 导入于 18A 制程,并与 RibbonFET 架构结合 2. 透过 nanoTSV 将背面供电网路连接至电晶体接触层 | 导入于 SF2Z 制程,并与 GAA(MBCFET)架构结合 |

技术影响:晶背供电带来供应链重塑

晶背供电技术的导入,对于台积电所处的全球半导体产业群体而言,不仅是一项制程突破,更可能重塑未来几年的市场结构与供应链配置。全球半导体市场正处于由 AI 需求主导的高速成长阶段,其中先进逻辑制程与高价 HBM 记忆体等高阶产品的需求是主要动能来源。这代表对超高性能晶片设计与制造的压力将持续上升,而背面供电等前沿架构技术正好对应这一需求环境。

从市场定位层面看,台积电在 A16 导入 Super Power Rail 等 BSPDN 架构,是因应 AI 加速器、HPC 平台与云端资料中心日益复杂的供电与能效要求,而非单纯追逐摩尔定律的线宽缩减。这一策略能在未来产品组合中向客户提供更佳的能效比与电源完整性设计空间,尤其是面对内建大规模运算与高带宽记忆体的晶片设计,SPR 的潜在价值不仅在于提升单颗晶片效能,更在于支撑市场对高阶应用的设计需求。

从供应链影响来看,晶背供电的广泛应用可能带动产业上下游结构性升级。 一方面,先进制程设备与材料需求将同步提升,涉及晶圆减薄、背面键合、高精度制程检测与先进封装等领域的厂商可能因技术门槛提高而获益。晶背供电与再生晶圆技术正推动制程材料与设备市场的需求加速,包括研磨耗材、乘载晶圆等高精密耗材的应用价值提升。这意味着台积电的技术选择不仅影响自身制造平台,也会透过供应链扩展带动相关产业的增量成长。

此外在全球供应链竞争与市场需求多元化的背景下,台积电在最先进制程持续领先,可强化其在高阶逻辑与 AI 晶片生产中的龙头地位,进一步凝聚客户阵营。 由于不同应用市场对 PPA 与可靠性要求显著提高,先进背面供电技术有望成为晶片设计不可或缺的一环,而能够提供高效能制程平台的代工厂将更具价格与议价空间。这种市场驱动下的技术导入,不仅强化台积电作为全球 Fab 1 角色的竞争优势,也可能促进其更紧密地参与全球高阶应用生态系整合。

综观整体产业趋势,在 AI 与 HPC 推升需求、先进制程占比提升的背景下,晶背供电等技术的落地将从系统需求端、供应链结构与制造竞争力共同推动市场格局变化,台积电若能在此领域持续保持技术与量产优势,其市场定位与长期营收结构有望进一步稳固与提升。

晶背供电技术受惠台厂

中砂(1560.TW)

中砂为半导体制程中 CMP 相关耗材的重要供应商,专注先进制程所需之精密研磨与平坦化耗材,产品涵盖钻石碟、砂轮及再生晶圆,主要应用于台积电等一线晶圆代工厂。 公司由传统砂轮起家,随取得钻石碟关键技术并配合台积电供应链在地化策略,成功转型为具研磨与切割核心能力的精密耗材制造商。其竞争优势在于钻石碟为 CMP 制程关键耗材、替代性低且具高认证门槛,并与台积电长期深度合作,于 3 奈米制程市占率约七成,同时具备钻石碟与再生晶圆的材料整合能力。

在 BSPDN 发展趋势下,中砂可望受惠于:

- 钻石碟需求具高度刚性,随 2 奈米制程量产推进,对平整度要求提升,月出货量已突破 5 万颗

- 先进制程研发带动再生晶圆需求,随制程验证与设备校正需求增加,挹注稳定成长动能。

整体而言,中砂在台积电供应链中具备高市占的钻石碟关键地位,并同时拥有再生晶圆制造优势,随先进制程推进,为台积电先进制程相关需求下的核心受益者之一。

升阳半导体(8028.TW)

升阳半导体为台湾长期深耕再生晶圆与晶圆薄化制程的晶圆材料提供商,专注于服务先进制程与高阶制造需求。 公司核心业务涵盖再生晶圆供应、晶圆薄化及相关材料处理技术,主要客户包含台积电等一线晶圆代工厂。其竞争优势主要来自与台积电长期合作所累积的制程理解与客户黏着度,以及在再生晶圆领域具备高度市占率与规模化量产能力。

在 BSPDN 技术发展趋势下,升阳半导体可望受惠于:

- 先进制程持续推进,设备校正与制程测试需求提升,带动再生晶圆使用量成长。

- 晶圆极端薄化与背面制程导入,制程中需透过暂时键合提供结构支撑,承载晶圆需求同步增加。

整体而言,升阳在再生晶圆领域具备高度市占地位,并深度参与台积电先进制程供应链,同时受惠于晶背供电导入下承载晶圆需求提升,为相关制程与材料需求成长的核心受益者之一。

天虹(6937.TW)

天虹科技为台湾首家具备半导体先进设备量产能力的本土设备商,产品涵盖物理沉积(PVD)、原子层沉积(ALD),以及晶圆键合(Bonder)/解键合(Debonder)设备,主要应用于半导体与化合物半导体制程。 其中,ALD 被视为实现高精度背面金属与介电层沉积的关键技术。其竞争优势为台湾少数具备先进制程前端设备量产能力的本土供应商,核心竞争力来自扎实的研发能力,使其设备布局自物理气相沉积、原子层沉积延伸至晶圆键合与解键合,形成相对完整的前端设备产品线,并能快速且精准回应客户需求,维持平均一年推出一项新设备的节奏。

在 BSPDN 技术发展趋势下,天虹科技可望受惠于:

- 先进制程前端设备国产化趋势推进,作为台湾少数可直接提供先进制程前端设备的本土厂商

- 晶背供电导入下,制程中对暂时键合(Temporary Bonding)与解键合(Debonding)设备的需求同步增加,进一步扩大其相关设备的应用空间。

整体而言,天虹为台湾少数具备先进制程前端设备量产能力的本土设备供应商,产品涵盖原子层沉积与物理气相沉积设备,并深度参与先进制程与晶背供电相关制程,受惠于暂时键合与解键合设备需求提升,为先进制程设备国产化趋势下的核心受益者之一。