在当前 AI 产业的热潮之中,由于晶片能带来算力,进而驱动对模型及相关应用的扩展,这使得企业对先进半导体技术的需求逐步增加。如同我们在 CoWoS 介绍中所提到的,在未来除了持续降低「闸极长度」外,也可以借由「先进封装」来增加晶片效能。今天我们就让 fiisual 来带你看看,究竟什么是 SoIC 封装,以及在未来可能有什么应用吧!

SoIC 封装是什么?

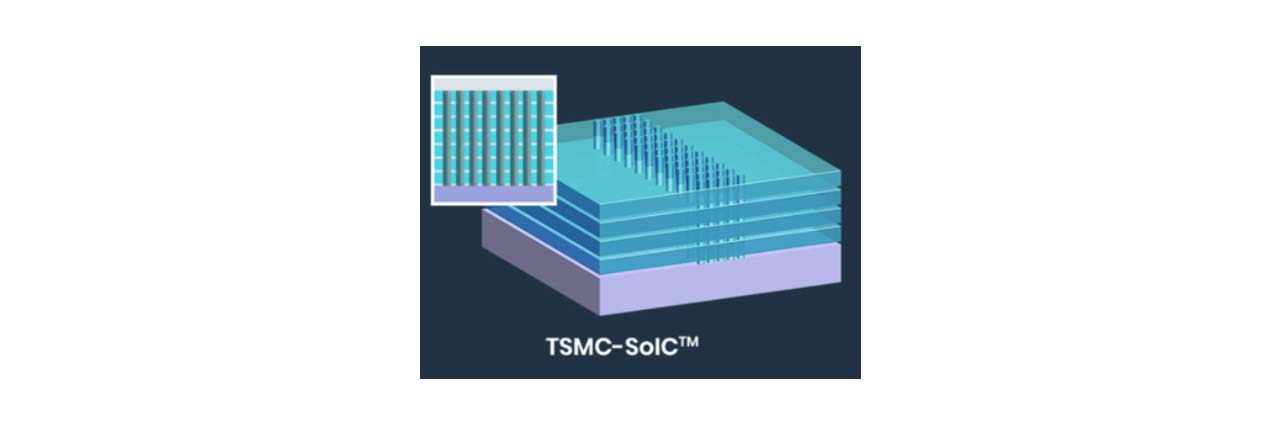

SoIC(System-on-Integrated-Chips)是一种由台积电(TSMC)开发的先进封装技术,专注于高密度的 3D 晶片堆叠。先前我们提到 CoWoS 可以归类在「2.5D」封装,也就是在下层将 PCB 板和中介板以垂直的方式叠合 (3D),上层的 SoC 晶片和 HBM 则以水平的方式排列 (2D),因此综合称为2.5D。

SoIC 是业界第一个高密度 3D 小晶片堆叠技术,其特别之处在于使用矽穿孔(TSV)取代传统金属端点堆叠的方式,在晶片上以化学蚀刻或雷射的方式钻孔,把所有晶片垂直堆叠在一起。这样的方式可以减少矽中介板的使用,进而缩小整体堆叠体积。

| CoWoS | SoIC | |

|---|---|---|

| 英文全名 | Chip-on-Wafer-on-Substrate | System-on-Integrated-Chips |

| 封装技术 | 2.5D | 3D |

| 目前使用情形 | 已经正式应用于产品中 | 目前仍在测试即持续研发中 |

不过因为要在晶片内直接制作矽穿孔的难度极高,此外,晶片与晶片或是晶圆与晶圆之间需要保持平整才能完全接合,此项技术的可靠度与良率仍有待提升,目前仍在测试和研发阶段。

SoIC 的技术特点

高密度堆叠

SoIC 技术未来的目标是达到每平方毫米 100 万个互连。封装堆叠技术提高,可以实现更高的计算能力和更快的数据传输速率,并缩小了整体的封装尺寸,整体而言也可以因讯号传送的距离缩短而减少功耗。

无凸点设计

SoIC 的设计不使用传统的凸点(bumps),而是采用混合键合(Hybrid Bonding)技术,这使得晶片之间的连接更加紧密,并且能有效提升散热性能。混合键合技术允许晶片之间直接进行铜对铜 (Cu-Cu) 的连接,无需使用凸点作为连接。这种方法使得晶片之间的连接更加紧密,可以实现更高的互连密度。

目前 SoIC 有提供两个不同的堆叠方案来满足不同的场景使用需求:

1. SoIC - P

使用微凸点的方式堆叠,适用于对成本敏感的产品,例如行动装置。

2. SoIC - X

使用无凸点的方式堆叠,适用于追求高效能运算的产品,可大量运用在人工智能相关的应用中。

多样化应用

SoIC 技术适用于 10 奈米及以下的先进制程,并在云计算、边缘计算和高性能计算(HPC)等领域具有广泛的应用潜力。举例来说,SoIC 技术可以提升计算效率和数据频宽,支持云计算中对高性能和低延迟的需求。另外,SoIC 技术的高密度互连和低功耗特性也非常适合于边缘计算应用,这包括自动驾驶汽车、增强现实和虚拟现实等需要快速响应的应用。

市场前景

随着半导体技术的发展,SoIC技术被认为是未来晶片设计和制造的重要趋势。台积电计划在 2025 年开始量产这项技术,并预期将在多个高需求领域中发挥关键作用,如自动驾驶汽车和 AI 伺服器。总的来说,SoIC 技术代表了晶片封装技术的一次重大进步,能够在保持小型化的同时,显著提升性能和效率。

虽然目前SoIC技术尚未发展成熟,仍处小量试产的阶段,但各个美国大厂已逐步与台积电商讨合作专案。其中AMD的MI300系列 AI GPU 和高阶游戏 CPU,以及苹果的 M5 晶片皆传出将在 2025 年跟进 SoIC 封装。目前 SoIC 月产能大约为 4 千片,预计明年将至少扩大一倍,而 2026 年产能将数倍以上成长。

相信聪明的你已经完全了解 SoIC 封装技术是什么了,还想看其他AI产业相关的文章了话,不要错过以下啦!